#gpiozero library

Wednesday, February 12, 2025

Thursday, January 30, 2025

fuzzy search

Below are from answers get from Deepseek

### **How Fuzzy Search Works**

Fuzzy search is designed to find strings that approximately match a given query, even if the query contains typos, misspellings, or incomplete words. The key idea is to rank potential matches based on how closely they align with the query.

#### Key Concepts:

1. **Subsequence Matching**:

- Fuzzy search looks for whether the characters in the query appear in the target string **in the same order**, but not necessarily consecutively.

- For example, the query `"leaders"` matches `"leadership skills"` because the letters `l`, `e`, `a`, `d`, `e`, `r`, `s` appear in order within the target string.

2. **Scoring**:

- Matches are ranked based on how closely they align with the query. Factors like:

- **Proximity of characters**: Characters that appear closer together in the target string are preferred.

- **Completeness**: Matches that include more of the query characters are ranked higher.

3. **Efficiency**:

- Fuzzy search algorithms are optimized to quickly filter and rank potential matches, even in large datasets.

---

### **How FuzzyFinder Implements Fuzzy Search**

FuzzyFinder uses a simple yet effective approach to implement fuzzy search. Here’s a high-level overview of how it works:

#### Algorithm Steps:

1. **Preprocessing**:

- Convert both the query and the target strings to lowercase (to make the search case-insensitive).

2. **Subsequence Matching**:

- For each target string, check if the characters in the query appear in the same order within the target string.

- Example:

- Query: `"leaders"`

- Target: `"leadership skills"`

- Check if `l`, `e`, `a`, `d`, `e`, `r`, `s` appear in order in `"leadership skills"`.

3. **Scoring**:

- Assign a score to each match based on:

- **Character proximity**: Characters that appear closer together in the target string are preferred.

- **Match completeness**: Matches that include more of the query characters are ranked higher.

4. **Ranking**:

- Sort the matches based on their scores and return the results.

---

### **Example Implementation of Fuzzy Search**

If you wanted to implement a simple version of fuzzy search yourself, here’s how you could do it in Python:

#### Code:

```python

def fuzzy_search(query, choices):

query = query.lower()

matches = []

for choice in choices:

choice_lower = choice.lower()

i = 0 # Index for query

j = 0 # Index for choice

score = 0

# Check if query characters appear in order in the choice

while i < len(query) and j < len(choice_lower):

if query[i] == choice_lower[j]:

i += 1

score += 1 # Increase score for each matching character

j += 1

# If all query characters were found in order, add to matches

if i == len(query):

matches.append((choice, score))

# Sort matches by score (higher scores first)

matches.sort(key=lambda x: x[1], reverse=True)

return [match[0] for match in matches]

# Example usage

terms = [

"team leaders",

"project leaders",

"leadership skills",

"manager",

"ceo",

"director",

"lead developer",

"head of department",

"lead engineer",

"leadership training"

]

query = "leaders"

matches = fuzzy_search(query, terms)

print("Fuzzy matches for 'leaders':", matches)

```

#### Output:

```

Fuzzy matches for 'leaders': ['team leaders', 'project leaders', 'leadership skills', 'leadership training']

```

---

### **Why FuzzyFinder is Efficient**

FuzzyFinder is optimized for performance. It avoids complex calculations (like Levenshtein distance) and instead focuses on **subsequence matching** and **scoring**, which makes it fast and suitable for real-time applications.

---

### **Comparison with Other Algorithms**

1. **Levenshtein Distance**:

- Measures the number of edits (insertions, deletions, substitutions) required to transform one string into another.

- More accurate but computationally expensive for large datasets.

2. **FuzzyWuzzy**:

- Uses Levenshtein distance and provides similarity scores.

- Slower than FuzzyFinder but more precise.

3. **Regular Expressions**:

- Can be used for pattern matching but doesn’t handle typos or approximate matches.

---

### **When to Use FuzzyFinder**

- When you need **fast, approximate matching** for large datasets.

- When you want a lightweight solution without heavy dependencies.

- When you don’t need the precision of Levenshtein distance.

---

### **Conclusion**

FuzzyFinder’s algorithm is not overly complicated—it relies on **subsequence matching** and **scoring** to efficiently find approximate matches. If you’re curious, you can even implement a basic version yourself (as shown above) to understand how it works under the hood.

If you’d like to dive deeper into the implementation or explore more advanced fuzzy search techniques, let me know! 😊

Sunday, April 28, 2024

C Programming

Header Files and Includes

Preprocessing Macros

Thursday, February 8, 2024

SVN Quick Reference

this is a short summary for my reference based on the great official tutorial at:

Basic Work Cycle (red-bean.com)

Check out a working copy from a repository

Update Your Working Copy

Make Your Changes

Changing the Repository Without a Working Copy

Review Your Changes

Fix Your Mistakes

Resolve Any Conflicts

Commit Your Changes

Examining History

%svn diff --summarize -r42:41 #just pirnt the filenames that has changes between 2 commitsCheckout a Specific Version of files

Sometimes You Just Need to Clean Up

Saturday, January 13, 2024

PCIe Study Notes

Chapter 1: Background

Nice References

PCI

PCI-X

Chapter 2: PCIe Architecture Overview

Transaction Layer

Data Link Lyaer

Physical Layer

Electriclal Part

Chapter 3: Configuration Overview

Enumeration

PCIe Devices: 32 devices per bus; PCIe point-to-point link means that device will always be Device 0. Deach Device must implement Function 0.

PCIe Functions: Functions do not need to be implemented sequenctially. SW must check every one of the 8 functions to decide which are present.

Errors should not normally be reported during enumeration.(the enumeration sw could fail since it's typically writtent o execute before the OS or other error handling SW is available.

Device not present: SW get Vendor ID of FFFFh, reserved for "device not present"

#TODO: enumeration started after 100ms+link training after reset, how to do it in DV simulation?

#TODO: what will enum sw do if there is no EP attached to a pci-pci bridge? #multi-root system: what if rc assign start bus number 64 to rc, but later find that the total buses are more then 265-64? is this an error? It is important to remember that each port on a switch is aBridge, and thus has its own configuration space with a Type 1 Header. In reality, each port (each P2P Bridge) has its own Type 1 Header and performs the same two checks on TLPs when they are seen by that port.

#TODO: enumeration started after 100ms+link training after reset, how to do it in DV simulation?

#TODO: what will enum sw do if there is no EP attached to a pci-pci bridge?

Chapter 4: Address Space & Transaction Routing

Confugration

TLP Routing

Saturday, August 19, 2023

TCP/IP Study Notes

TCP/IP segmentation and fragmentation:

reference link: 【计算机网络】区分tcp分段和ip分片 - JoyoHub

Virtualbox Settings Reference

Networking Settings

to record issues when setting up different network options for my guest linux virtual machine.

refernce link: 【计算机网络】:一次性理清Virtualbox虚拟机网络模型 - JoyoHub

reference link: https://www.nakivo.com/blog/virtualbox-network-setting-guide/

1. issues when usign Bridged Adapter mode.

cannot get ipv4 address

set to NAT mode first, and get ip address by checking ifconfig

then switch to Bridged Adapter mode, and very importantly, choose the correct NIC (if you are using wifi, choose the wireleass NIC! in my case default is ehterent NIC, and i must change it to my wifi NIC), then check the ip address now using ifconfig. it works for me!

Extension Pack Installation

Enable USB

Monday, June 26, 2023

Traffic Management

Rate Limiting

Refer: https://hansliu.com/posts/2020/11/what-is-token-bucket-and-leaky-bucket-algorithms.html

1. Token bucket

- Rate Limiting: produce rate of token

- Bucket Sizes: number of token

- Token Check: if token valid, process data

2. leaky bucket

- Rate Limiting: consume rate of data

- Bucket Sizes: number of data

Queueing QoS

WFQ, FQ, WRR

http://what-when-how.com/qos-enabled-networks/queuing-and-scheduling-qos-enabled-networks-part-1/

Monday, January 11, 2021

Systemverilog Assertion Notes

refer to: Dulos SVA tutorial

I) Immediate Assertions

Guideline: Avoid using immediate assertions

assert (A == B); // Asserts that A equals B; if not, an error is generated

assert (A == B) $display ("OK. A equals B");

assert (A == B) $display ("OK. A equals B"); else $error("It's gone wrong");

assert (A == B) else $error("It's gone wrong");

The failure of an assertion has a severity associated with it: $fatal, $error (the default severity) and $warning. In addition, the system task $info indicates that the assertion failure carries no specific severity.

Igt10: assert (I > 10) else $warning("I is less than or equal to 10");

The pass and fail statements can be any legal SystemVerilog procedural statement.

AeqB: assert (a === b) else begin error_count++; $error("A should equal B"); end

II) Concurrent Assertions

Guideline: Use concurrent assertions

Guideline: Use long, descriptive labels to your assertions code, (a) documents the assertions, and (b) accelerates debugging using waveform displays.

Guideline: Use label names that start with "ERR" or "ERROR" and then include a short sentence to describe what is wrong if that assertion is failing.

Properties are built using sequences. For example,

assert property (@(posedge Clock) Req |-> ##[1:2] Ack);

where Req is a simple sequence (it’s just a boolean expression) and ##[1:2] Ack is a more complex sequence expression, meaning that Ack is true on the next clock, or on the one following (or both). |-> is the implication operator, so this assertion checks that whenever Req is asserted, Ack must be asserted on the next clock, or the following clock.

Concurrent assertions like these are checked throughout simulation. They usually appear outside any initial or always blocks in modules, interfaces and programs. (Concurrent assertions may also be used as statements in initial or always blocks. A concurrent assertion in an initial block is only tested on the first clock tick.)

III) Implications

Guideline: Use |-> ##1 implications and not |=> implications.

|-> tests for a valid consequenct expression in the same cycle.

|=> tests for a valid consequenct expression in the next cycle.

IV) Properties and Sequences

Properties and Sequences In these examples we have been using, the properties being asserted are specified in the assert property statements themselves. Properties may also be declared separately, for example:

property not_read_and_write; not (Read && Write); endproperty assert property (not_read_and_write);

Complex properties are often built using sequences. Sequences, too, may be declared separately:

sequence request Req; endsequence sequence acknowledge ##[1:2] Ack; endsequence property handshake; @(posedge Clock) request |-> acknowledge; endproperty assert property (handshake);

V) Assertion Clocking

The clock for a property can be specified in several ways:

Explicitly specified in a sequence:

sequence s; @(posedge clk) a ##1 b; endsequence property p; a |-> s; endproperty assert property (p);

Explicitly specified in the property:

property p; @(posedge clk) a ##1 b; endproperty assert property (p);

Explicitly specified in the concurrent assertion: assert property (@(posedge clk) a ##1 b);

Inferred from a procedural block:

property p; a ##1 b; endproperty always @(posedge clk) assert property (p);

From a clocking block (see the Clocking Blocks tutorial):

clocking cb @(posedge clk); property p; a ##1 b; endproperty endclocking assert property (cb.p);

From a default clock (see the Clocking Blocks tutorial):

default clocking cb;

VI) Handling Asynchronous Resets

In the following example, the disable iff clause allows an asynchronous reset to be specified.

property p1;

@(posedge clk) disable iff (Reset) not b ##1 c;

endproperty

assert property (p1);

The not negates the result of the sequence following it. So, this assertion means that if Reset becomes true at any time during the evaluation of the sequence, then the attempt for p1 is a success. Otherwise, the sequence b ##1 c must never evaluate to true.

VII) Sequences

A sequence is a list of boolean expressions in a linear order of increasing time. The sequence is true over time if the boolean expressions are true at the specific clock ticks. The expressions used in sequences are interpreted in the same way as the condition of a procedural ifstatement. Here are some simple examples of sequences.

The ## operator delays execution by the specified number of clocking events, or clock cycles.

a ##1 b // a must be true on the current clock tick // and b on the next clock tick

a ##N b // Check b on the Nth clock tick after a

a ##[1:4] b // a must be true on the current clock tick and b // on some clock tick between the first and fourth // after the current clock tick

The * operator is used to specify a consecutive repetition of the left-hand side operand.

a ##1 b [*3] ##1 c // Equiv. to a ##1 b ##1 b ##1 b ##1 c

(a ##2 b) [*2] // Equiv. to (a ##2 b ##1 a ##2 b)

(a ##2 b)[*1:3] // Equiv. to (a ##2 b) // or (a ##2 b ##1 a ##2 b) // or (a ##2 b ##1 a ##2 b ##1 a ##2 b)

The $ operator can be used to extend a time window to a finite, but unbounded range.

a ##1 b [*1:$] ##1 c // E.g. a b b b b c

The [-> or goto repetition operator specifies a non-consecutive sequence.

a ##1 b[->1:3] ##1 c // E.g. a !b b b !b !b b c

This means a is followed by any number of clocks where c is false, and b is true between 1 and three times, the last time being the clock before c is true.

The [= or non-consecutive repetition operator is similar to goto repetition, but the expression (b in this example) need not be true in the clock cycle before c is true.

a ##1 b [=1:3] ##1 c // E.g. a !b b b !b !b b !b !b c

VIII) Combining Sequences

There are several operators that can be used with sequences:

The binary operator and is used when both operand expressions are expected to succeed, but the end times of the operand expressions can be different. The end time of the end operation is the end time of the sequence that terminates last. A sequence succeeds (i.e. is true over time) if the boolean expressions containing it are true at the specific clock ticks.

s1 and s2 // Succeeds if s1 and s2 succeed. The end time is the // end time of the sequence that terminates last If s1 and s2 are sampled booleans and not sequences, the expression above succeeds if both s1 and s2 are evaluated to be true.

The binary operator intersect is used when both operand expressions are expected to succeed, and the end times of the operand expressions must be the same.

s1 intersect s2 // Succeeds if s1 and s2 succeed and if end time of s1 is // the same with the end time of s2

The operator or is used when at least one of the two operand sequences is expected to match. The sequence matches whenever at least one of the operands is evaluated to true.

s1 or s2 // Succeeds whenever at least one of two operands s1 // and s2 is evaluated to true

The first_match operator matches only the first match of possibly multiple matches for an evaluation attempt of a sequence expression. This allows all subsequent matches to be discarded from consideration. In this example:

sequence fms;

first_match(s1 ##[1:2] s2);

endsequence

whichever of the (s1 ##1 s2) and (s1 ##2 s2) matches first becomes the result of sequence fms.

The throughout construct is an abbreviation for writing:

(Expression) [*0:$] intersect SequenceExpr

i.e. Expression throughout SequenceExpr means that Expression must evaluate true at every clock tick during the evaluation of SequenceExpr.

The within construct is an abbreviation for writing:

(1[*0:$] ##1 SeqExpr1 ##1 1[*0:$]) intersect SeqExpr2

i.e. SequenceExpr1 within SequenceExpr2 means that SeqExpr1 must occur at least once entirely within SeqExpr2 (both start and end points of SeqExpr1 must be between the start and the end point of SeqExpr2).

IX) Variables in Sequences and Properties

Variables can be used in sequences and properties. A common use for this occurs in pipelines:

`define true 1

property p_pipe;

logic v;

@(posedge clk) (`true,v=DataIn) ##5 (DataOut === v);

endproperty

In this example, the variable v is assigned the value of DataIn unconditionally on each clock. Five clocks later, DataOut is expected to equal the assigned value. Each invocation of the property (here there is one invocation on every clock) has its own copy of v. Notice the syntax: the assignment to v is separated from a sequence expression by a comma, and the sequence expression and variable assignment are enclosed in parentheses.

X) Coverage Statements

In order to monitor sequences and other behavioural aspects of a design for functional coverage, cover property statements can be used. The syntax of these is the same as that of assert property. The simulator keeps a count of the number of times the property in the cover property statement holds or fails. This can be used to determine whether or not certain aspects of the designs functionality have been exercised.

module Amod2(input bit clk);

bit X, Y;

sequence s1; @(posedge clk) X ##1 Y; endsequence

CovLavel: cover property (s1);

...

endmodule

SystemVerilog also includes covergroup statements for specifying functional coverage. These are introduced in the Constrained-Random Verification Tutorial.

XI) Assertion System Functions

SystemVerilog provides a number of system functions, which can be used in assertions. $rose, $fell and $stable indicate whether or not the value of an expression has changed between two adjacent clock ticks. For example,

assert property (@(posedge clk) $rose(in) |=> detect);

asserts that if in changes from 0 to 1 between one rising clock and the next, detect must be 1 on the following clock. This assertion,

assert property (@(posedge clk) enable == 0 |=> $stable(data));

states that data shouldn’t change whilst enable is 0.

The system function $past returns the value of an expression in a previous clock cycle. For example,

assert property (@(posedge clk) disable iff (reset) enable |=> q == $past(q+1));

states that q increments, provided reset is low and enable is high. Note that the argument to $past may be an expression, as shown above.

The system functions $onehot and $onehot0 are used for checking one-hot encoded signals. $onehot(expr) returns true if exactly one bit of expr is high; $onehot0(expr) returns true if at most one bit of expr is high.

assert property (@(posedge clk) $onehot(state));

There are other system functions.

XII) Binding

Guideline: bindfiles, use them!

Guideline: Use the bind command style that binds to all DUT modules, not the bind style that only binds to specified instances.

a) bind to all instances of a module

bind fifo1 fifo1_asserts p1 (.*);

b) bind to specific DUT instance with or without using the module name

Guideline: do not use these styles.

c) bindfiles for parameterized modles

d)bindfiles with .* port connections

Wednesday, November 4, 2020

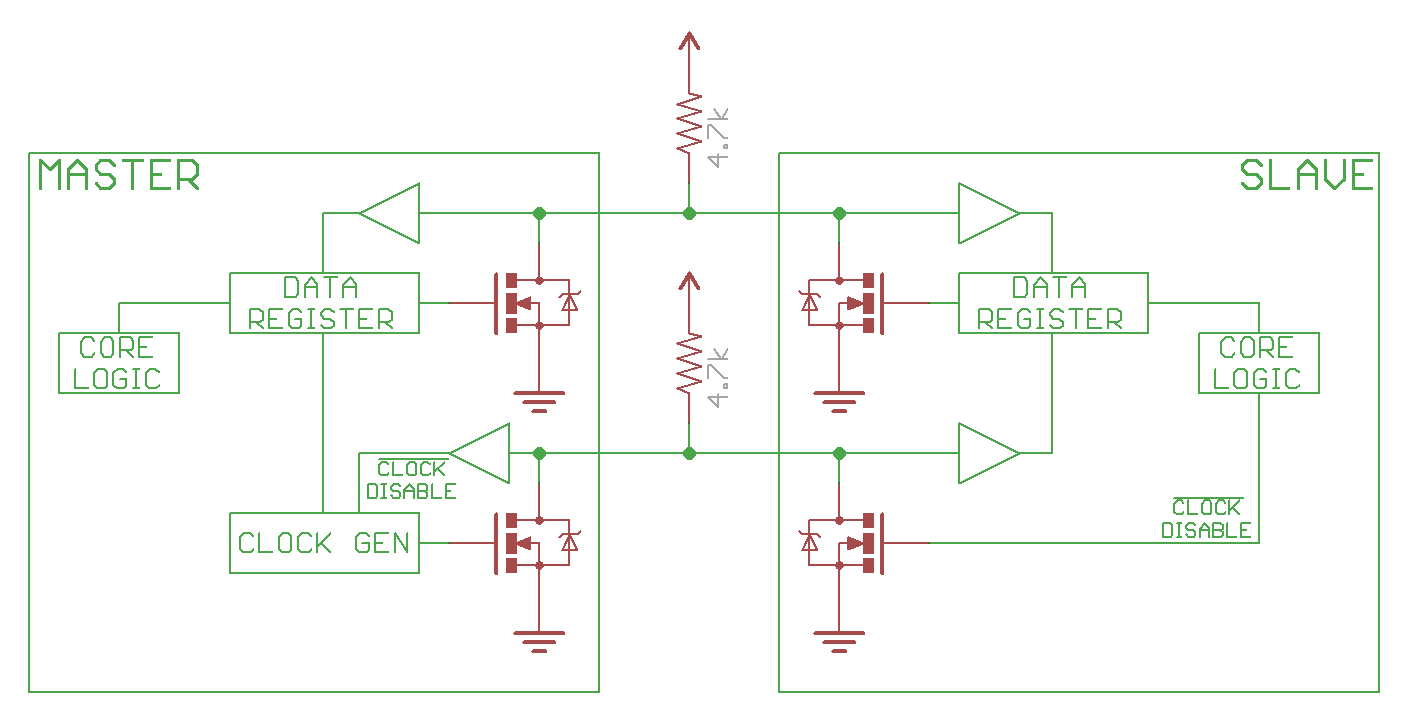

I2C IIC Tutorial

1. The Protocol

Resolving address conflicts: https://embeddedartistry.com/blog/2021/08/02/resolving-i2c-address-conflicts/

Sunday, August 2, 2020

PRBS using linear feedback shift register implemented in Python

Friday, May 8, 2020

Photoshop

Affinity Photo with pen tablet:

Ctrl+Alt(option)+drag: left/right for brush size, up/down for hardness

Spacebar+Cmd+drap: left/right zoom out/in

Cmd+0: zoom to fit window

B: brush tool

J: healing brush

J: spot healing brush

S: clone stamp

H: hand tool(view)

New Layer: Shift+Cmd+N

Tuesday, December 10, 2019

questions

how to match non empty strings between two elements?

[Python] what is difference between re.search(), re.match() and re.findall(), when to use each of them?

[Python] how to execute multiline code in the python interpreter? use backslashes to continue on the next line

[Python] how to test if a variable is empty string or contains only space or is none? if a or a.strip(), this will first test if it's None, then test if it only contains spaces, tabs, newlines and so on.

[Python] how to test if a variable is True, False, or None?

test True: if a is True

#if a is a non-zero number, a will evaluate to true, but a number is not the same as boolean True! keep in mind of this.

test None: if a is None

#None is a special singleton object, there can only be one. Just check to see if you have that object.

test False: a not True and not None, then it's

[Python] how to check if a variable is a string?

method a: isinstance(a, str)

The isinstance function takes two arguments. The first is your variable. The second is the type you want to check for. in Python 3.x, all types are classes.

method b: if type(a) == str:

use the type built-in function to see the type of variables. None:'NoneType', booleans:'bool', strings:'str', numbers:'int','float', lists:'list', tuples:'tuple', dictionaries:'dict', ...

Thursday, October 10, 2019

Systemverilog simulators related

performance profile

VCS:profile in VCS by time or memory.

#for memory profiling

-simproile //compile option

-simprofile mem //simulation option

#for time profiling

-simprofile //compile options

-simprofile time //sim options

the profile report will be store at compile directory named "profilereport"

IUS:

debug sim hang by using cpu usage report

compile option: -linedebug

simulation option: -profile

at sim hang point, stop test by: Ctrl+c (1 time), then ncsim>exit

check the ncprof.out file (cpu usage summary and source code location)

Coverage

code coverage fefinition:line/statement: will not cover module/end module/comments/time scale

block: begin...end, if...else, always

expression:

branch: case

conditional: if...else, ternary operator (?:)

toggle:

FSM:

VCS:

%vcs -cm line+tgl+branch source.v

%simv -cm branch

vcs urg (Unified Report Generator):

%urg -dir simv1.vdb [simv2.dir simv3.vdb ...] -metric line+cond+branch -report specified_ouput_dir //general options

%urg ... -parallel -sub bsub -lsf "" //run urg in parallel to speed up

%urg -elfile <filename> //for exclusion files

%dve -covdir simv.vdb//view coverage db directly in DVE

Dump Waveform

setenv FSDB_FORCE //to display forced signals in highlight in waveform viewer

2. sdf

3. use do file to control fsdb dump.

%vcs -ucli -do PATH_OF_DO_FILE //simulation options

below is a sample tcl do file:

####start of file###############

#control fsdb dump

set run_time_before_dump 0us

set dump_all 1

set run_time 400us

run $run_time_before_dump

set TOP eth_top_tb

fsdbDumpfile $TOP.fsdb

if (dump_all == 1) {

fsdbDumpvars 3 $TOP

fsdbDumpvars 0 $TOP.xxx...

fsdbDumpMDA 1 $TOP...

} esel {

...

}

run $run_time

exit

####end of file################

4.dump force information

Race Condition

Monday, September 30, 2019

Physical layer of Networking Hardware

prbs generator:

Random bit sequence using Verilogprbs polynomials used in networking

Fibonacci form and Galois form

Fibonacci form: Another unique feature to this form is that the values in the shift register aren’t modified between when they are originally calculated and the output–making it possible to see then next LN output bits by just examining the shift register state.

References:

wiki

Generating Pseudo-Random Numbers on an FPGA

An example LFSR

ADC OSC(oversampling ratio):

The basics of sigma delta analog-to-digital convertersDelta-sigma modulation

Explaining SerDes:

(Chinese) SerDes Knowlege: notice the limitations of parallel transmission.

circuit noises:

simultaneously switching noise an overview/Sunday, September 8, 2019

Tuesday, August 27, 2019

Digital Design Verification Subsystem Lessons Learned

- make bus randomized during invalid cycle, to catch dut bugs that did not check valid signals. However, the constraint should still give 0 bus value a weight, so that 0 bus value can happen in invalid cycle, just in case that in real chip, the bus value is gated to 0 by upper layer module.

- bugs of features that cross two subsystems are difficult to catch. if a value generated in one module, and will be used in next module, it has a higher chance to have bug uncatched, as it needs correct model behavior as real hardware. solution: a) it's better to try to implement this in the same module, instead of split it into different modules, if possible. an example is the idle insertion/deletion to accommodate the AM (alignment marker) insertion/deletion in PCS. in this case, it's better to implement it in PCS instead of in MAC.

- bugs of features that related to performance AND cross two subsystems are extremely difficult to catch. possible solutions: a) in subsystem level, force to speed up counter value count, and increase pkt counts and so on, so that the possibility is increased. however, this needs very specific test scenarios; b) use hardware acceleration or e, e.g. Palladium or Synopsys ZeBu; c) chip top test to simulate the cross subsystem behaviors

- simplify architecture based on real application. sometimes, smart design means simple brutal force. this one needs the architects sensitivity to the industry use scenarios. I have two examples: a) initially we design our switch to have all kinds of protocols and features to both be legacy device compatible and also includes new features. this leads to overdesign and many bugs (insufficient man power and verification time). however, data center ethernet switch are more focused on feed and speed, it needs high throughput, less focused on protocols. end results, a lot of features are not used, a lot of hot new architectures (like SDN) are not used. this is big waste of resources. b) ...?

- Review every registers with DE in review meetings. Need to decide for every register: a) what is its meaning and actual use case (e.g. how does software guy config it, how does SA test it in real chip); b) can it be randomized in base test or should be tested in specific test; c) does it have some values that are often used by SA and Customer in real chip? weighted distribution?

- Review base config randomization constraints for base test. this is also related to 5) as some of the configs are registers. it needs designer and SA's input to confirm.

- simulation time vs packets number: Do Not trade packets number for simulation time. Meaning that do not try to save hardware resources. For verification, the first priority is function correctness, and the more packet number, the more possible that a bug will be hit. CPU resources are cheap, real chip bugs are expensive!

- random noise register/memory access during every test. But make sure that the noise and actually traffic can actually hit the same register/memory to trigger corner bugs.

- there should be 2 types of checker for a features if it cannot be accurately checked in every scenarios: a) a specific test that accurately check it's function; b) a general checker which is enabled in every testcase, and act as a sanity checker, in case there is some fundamental bugs in certain corner cases, which was not found in the a).

- choose the constraint range carefully, and choose the random value carefully. speed mode, pkt number, and the event happen time are all related, need to consider them when setting constraint or randomization range.

- have status and counters for monitors and controlling tb in cfg or virtual interface. for example, have counter count received pkt count, or have status variable to monitor dut is in transmiting or idle state, and so on.

Tuesday, August 20, 2019

Protocols

– Bus topology / routing / resources:

From this point of view, I²C is a clear winner over SPI in sparing pins, board routing and how easy it is to build an I²C network.

– Throughput / Speed:

If data must be transferred at ‘high speed’, SPI is clearly the protocol of choice, over I²C. SPI is full-duplex; I²C is not. SPI does not define any speed limit; implementations often go over 10 Mbps. I²C is limited to 1Mbps in Fast Mode+ and to 3.4 Mbps in High Speed Mode – this last one requiring specific I/O buffers, not always easily available.

– Elegance:

Both SPI and I2C offer good support for communication with low-speed devices, but SPI is better suited to applications in which devices transfer data streams, while I²C is better at multi master ‘register access’ application.

Conclusions.

In the world of communication protocols, I²C and SPI are often considered as ‘little’ communication protocols compared to Ethernet, USB, SATA, PCI-Express and others, that present throughput in the x100 megabit per second range if not gigabit per second. Though, one must not forget what each protocol is meant for. Ethernet, USB, SATA are meant for ‘outside the box communications’ and data exchanges between whole systems. When there is a need to implement a communication between integrated circuit such as a microcontroller and a set of relatively slow peripheral, there is no point at using any excessively complex protocols. There, I²C and SPI perfectly fit the bill and have become so popular that it is very likely that any embedded system engineer will use them during his/her career.

2. RTC (Real-Time Clock)3. UART(Universal Asynchronous Receiver/Transmitter)

freebsd Serial and UART Tutorial

The Start bit always has a value of 0 (a Space). The Stop Bit always has a value of 1 (a Mark). This means that there will always be a Mark (1) to Space (0) transition on the line at the start of every word, even when multiple word are transmitted back to back. This guarantees that sender and receiver can resynchronize their clocks regardless of the content of the data bits that are being transmitted. refer to stm32f103 reference manual S.27.3.3: 16X oversampling was used to detect noise errors.

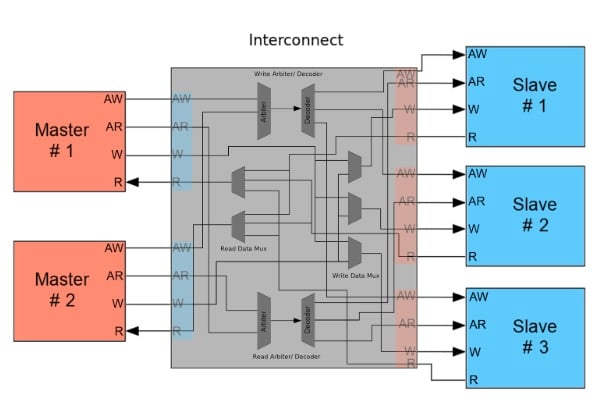

4. ARM AMBA

Burst len, size, type:

Out of order:

Interleave:

Unaligned Address:

AXI response

MIB RFC:

RFC2819 : Remote Network Monitoring Management Information Base

RFC2863: The Interfaces Group MIB

RFC3273: Remote Network Monitoring Management Information Base for High

RFC4836: Definitions of Managed Objects for IEEE 802.3 Medium Attachment Units (MAUs)

RFC3635: Definitions of Managed Objects for the Ethernet-like Interface Types

PFC MIB counter

Networking Protocols:

1. What is the exact difference between SGMII and 1000Base-X?

raspberry pi gpio controls

#gpiozero library https://gpiozero.readthedocs.io/en/stable/#

-

refer to the following links, I am just adding some corrections to the original post: https://coderwall.com/p/fy7stg/vim-and-systemverilog...

-

performance profile VCS: profile in VCS by time or memory. #for memory profiling -simproile //compile option ...

-

This article is to list down the most used constructions of UVM to my personal understanding. UVM simulator steps VCS(Synopsys) IUS(Ca...